SK���̴н��� ���� ���ʷ� JEDEC(�����ݵ�üǥ�����DZⱸ) ���� ������ DDR5 DRAM ���� ����� �˷ȴ�.

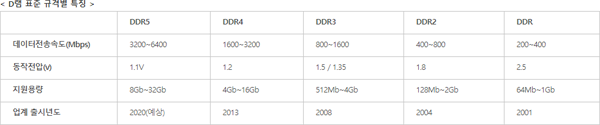

DDR5�� DDR4�� �մ� ������ D�� ǥ�ر�����, SK���̴н��� �ֱ� ������ 2���� 10�����(1y) 8Gbit(�Ⱑ��Ʈ) DDR4�� �̾�, ������ �̼������� ������ 16Gbit DDR5�� �ֿ� Ĩ�� ��ü�� ���������ν� ���踦 �����ϴ� ���������� Ȯ���� �� �ְ� �Ǿ��ٰ� �����ߴ�.

SK���̴н��� ���߿� ������ DDR5 DRAM�� ���� ������ DDR4 ��� ���� ������ 1.2V���� 1.1V�� ������ ���� �Һ��� 30% ������ �ݸ�, ���� �ӵ��� 3200Mbps���� 5200Mbps�� 1.6�� ���� ���ƴ�. �̴� FHD(Full-HD)�� ��ȭ(3.7GByte) 11���� �ش�Ǵ� 41.6GByte(�Ⱑ����Ʈ)�� ������ 1�ʿ� ó���� �� �ִ� �����̴�.

�̹��� Ĩ�� ��ü�� ������ ��ǰ�� ������ PC�� RDIMM(Registered Dual In-line Memory Module)�� UDIMM(Unbuffered DIMM)����, JEDEC DDR5 ǥ�ؿ� ���� ������ �����ϴ� �� ������ ���� ���� ������ 16�� ���� 32���� Ȯ���ϰ�(16bank → 32bank) �ѹ��� ó���ϴ� �������� ���� 8������ 16��(BL8 → BL16)�� �÷ȴ�. ���� �ý����� �ŷڼ� ����� ���� Ĩ ���ο� �������� ȸ��(Error Correcting Code)�� ����Ǿ� �ִ�.

�ʰ��� ���� Ư���� Ȯ���ϱ� ���� DRAM�� �б�/���� ȸ�θ� ������ ���·� �����ϴ� ���� Ʈ���̴� ���(high speed training scheme), ���� ������ �����ϴ� DFE(Decision Feedback Equalization), ���ɾ� �� ������ ó���� ����ȭ �ϱ� ���� 4������ Ŭ��ŷ(4phase clocking), �б� �������� �ְ��̳� ������ �ּ�ȭ�ϱ� ���� ������/������ DLL(Delay locked loop) �� DCC(Duty Cycle Correction)ȸ�� ���� �ű���� ä��Ǿ���.

���� ���������� IDC�� 2020����� DDR5 ���䰡 ���������� ���ϱ� ������ 2021��� ��ü D�� ������ 25%, 2022��� 44%�� ���� Ȯ��� ������ �����ߴ�.

|