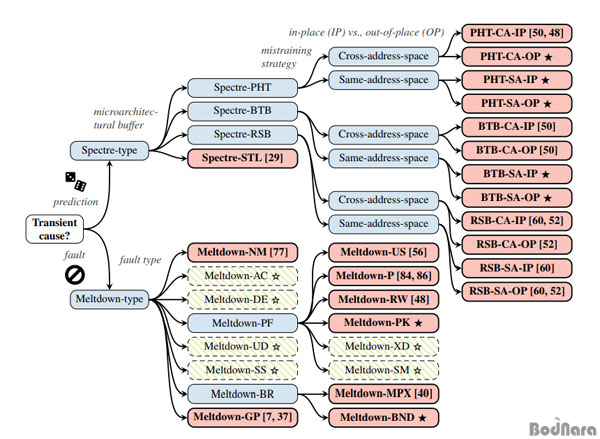

���� �� ���� ��ǥ�� CPU ���� ������� ��Ʈ�ٿ�� �����ʹ� ���� �� ������ ������ �߰ߵǾ�Դµ�, 9�� ������ ���� �������� 7���� ���ο� ������ �߰��ߴ�.

���Ӱ� �߰ߵ� 7���� ���� ����� �� 2���� ��Ʈ�ٿ�, 5���� �������� ��������, �������� ���� ���� �ڵ带 �̿��Ͽ� �̵� ������� ���輺�� �����ߴ�.

�ű� �߰ߵ� ��Ʈ�ٿ� ������� ���� �� AMD���� x86 �ٿ�� ���ɾ� ��� �����, ���� CPU������ �� ���� Ű ��ȸ�� ����ϸ�, ������ ������� CPU ���� ��� ���̺�/ CPU ���� ��� ����/ CPU ���� ���� ����/ CPU �б� ��� ���۸� �ǿ��Ѵ�.

����, �������� ���� ��� ���̺�(Patter History Table) ��Ŀ���� ����� �� ������ ���ο� ������ ���� ������ �б� Ÿ�� ����(Brach Target Buffer)�� ���� �� ������ ���ο� ������ ���� ����� ã�� ������, �̵� ���� ����� ���ڰ� AMD, ARM CPU�� ��ȿ�ϴ�.

����, �������� �̹��� ���Ӱ� �߰ߵ� 7���� ���� ������� �̷л� ������ �Ϻ� ��ȭ ��ġ�� ������� ���ϴٴ� �ǰ��� ������, ������ �߰����� ������ �ʿ��� ������ ����ȴ�.

|